# **Chip Scale Review**<sup>®</sup>

ChipScaleReview.com

## The Future of Semiconductor Packaging

Volume 29, Number 2

March • April 2025

Glass-based interposer for co-packaged optics

- New package solutions for automotive optical sensors

- Reliability challenge of underfills in large-size HI FO-MCM packages

- Impact of BGA solder metallurgy on BLR failure modes in FC packaging

- Dual damascene process for a 500nm RDL using a high-resolution photosensitive polymer

- Direct laser reflow techniques for stable and reliable solder bump interfaces on semiconductor substrates

**OK Pins**

in 7 Days

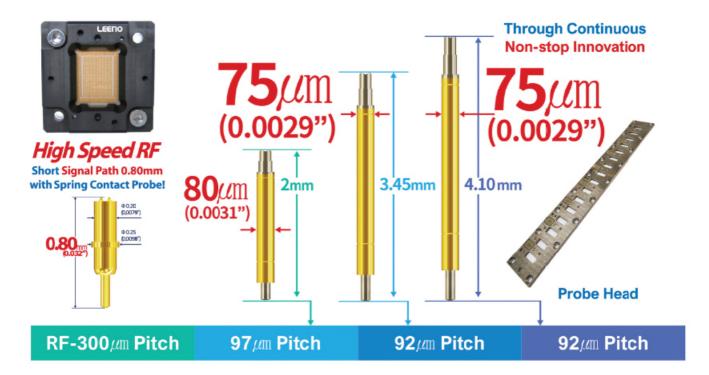

# Fine Pitch Probe & Probe Head

**Proven Mass Production Capability**

# 5G MP 100GHz Coaxial Socket

hskang@leeno.co.kr / +82 10 8737 6561 kimmj@leeno.co.kr / +82 10 5314 6560

# CONTENTS

Advanced packaging substrates, such as glass-based interposers combined with automated packaging processes, can overcome manufacturing bottlenecks in photonic component assembly. This approach will enable photonic and electronic co-packaged subsystems to scale to large-volume production. As a result, mass market demands--including data center communications, artificial intelligence, sensing and diagnostics--will be addressed. The cover image shows the packaging of a microlens array to a flip-chip assembled InP photonic integrated circuit on a glass electrical interposer with BGA contacts. Cover photo courtesy of Tyndall National Institute

## FEATURE ARTICLES

6 Co-packaging of photonic and electronic ICs on glass interposers By Peter O'Brien, Das Kumar [Tyndall National Institute]

#### Impact of BGA solder metallurgy on BLR failure modes in flip-chip packaging 14 By Jaimal Williamson, Yutaka Suzuki [Texas Instruments]

72 Reliability challenge of underfills in large-size heterogeneous integration FO-MCM packaging By Liang-Yih Hung, Chia-Wei Chang, Wen-Yu Teng, Andrew Kang, Yu-Po Wang [Siliconware Precision Industries Co., Ltd]

## New package solutions for automotive optical sensors

By Weilung Lu, Adrian Arcedera, WonBae Bang, KiDong Sim [Amkor Technology, Inc.]

www.EVGroup.com

1 D D

# IR LayerRelease<sup>™</sup> Technology

- **Replacement for mechanical debonding thanks to through-silicon IR laser**

- Enabling ultra-thin film or layer transfer from silicon carriers

- Nanometer-precision release of bonded, deposited or grown layers

- Front-end compatibility through silicon carriers and inorganic release materials

- Supporting future roadmaps in advanced packaging and transistor scaling

GET IN TOUCH to discuss your manufacturing needs www.EVGroup.com

EVG<sup>®</sup>880 LayerRelease™

# CONTENTS

# Chip Scale Review

STAFF Kim Newman Publisher knewman@chipscalereview.com

**Lawrence Michaels Managing Director** Editor-in-Chief Imichaels@chipscalereview.com

**Debra Vogler** Senior Technical Editor debravogler@me.com

#### SUBSCRIPTION-INQUIRIES

**Chip Scale Review** All subscription changes, additions, deletions to any and all subscriptions should be made by email only to subs@chipscalereview.com

Advertising Production Inquiries: Lawrence Michaels Imichaels@chipscalereview.com

Copyright © 2025 Haley Publishing Inc. Chip Scale Review is a registered trademark of Haley Publishing Inc. All rights reserved.

Subscriptions in the U.S. are available without charge to qualified individuals in the electronics industry. Chip Scale Review is published six times a year with issues in January-February, March-April, May-June, July-August, September-October and November-December

P.O. Box 2165 Morgan Hill, CA 95038 Tel: +1-408-846-8580 E-Mail: subs@chipscalereview.com

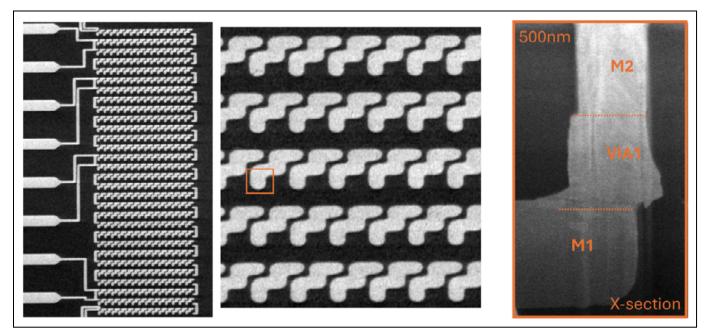

Printed in the United States

## FEATURE ARTICLES (continued)

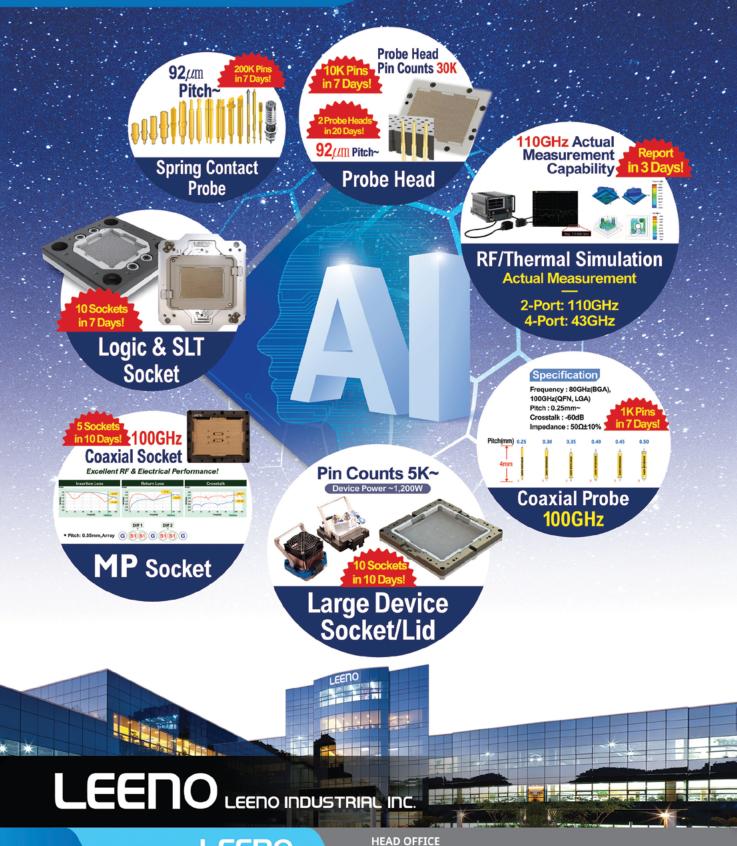

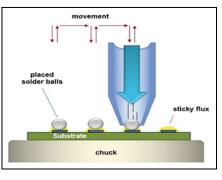

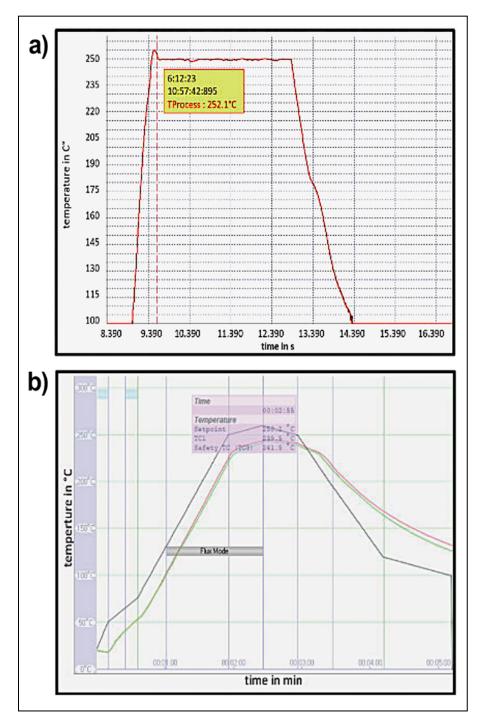

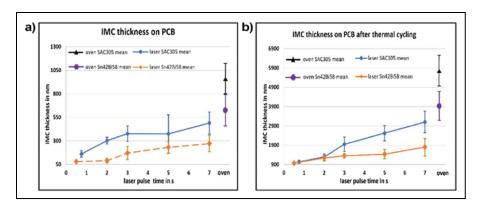

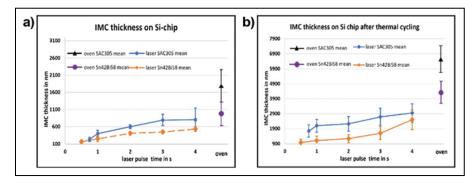

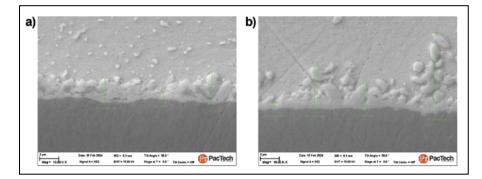

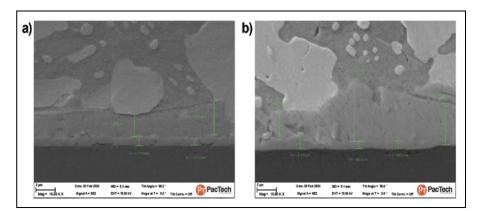

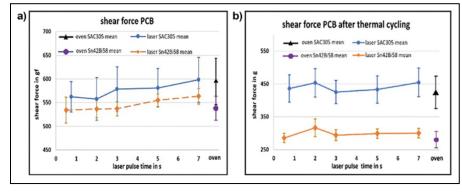

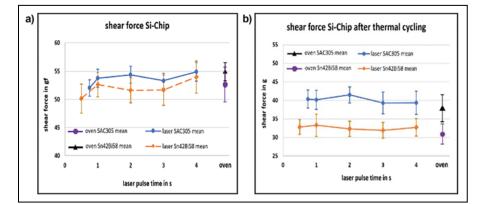

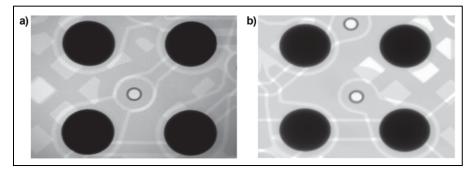

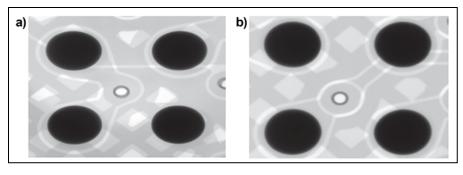

Direct laser reflow techniques for stable and reliable 38 solder bump interfaces on semiconductor substrates

By Matthias Fettke, Anne Fisch, Thorsten Teutsch [PacTech – Packaging Technologies GmbH]

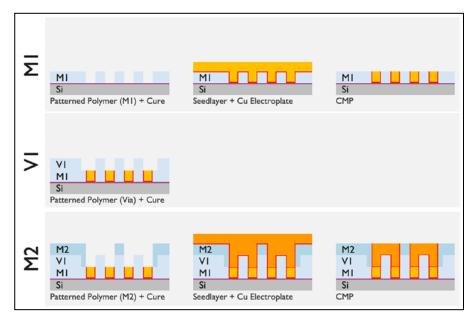

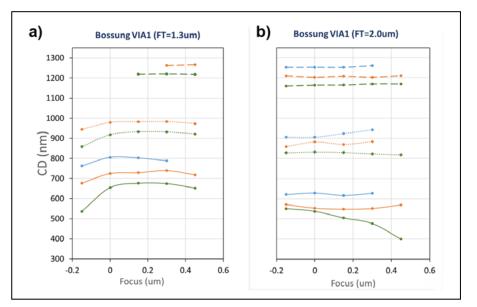

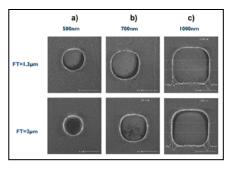

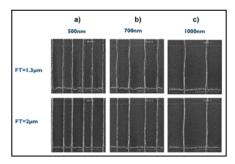

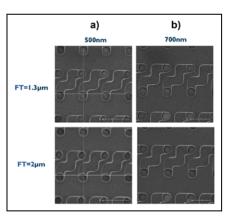

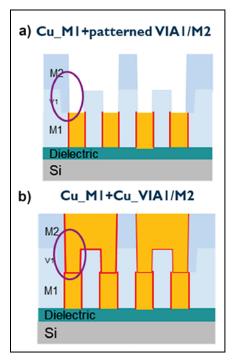

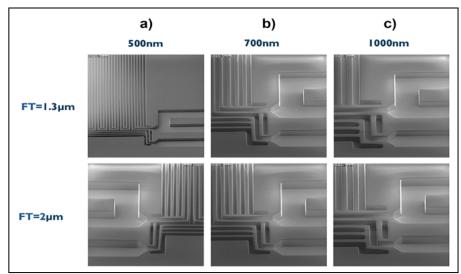

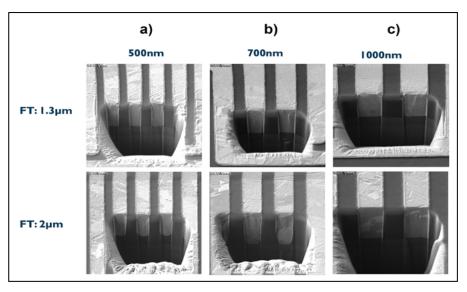

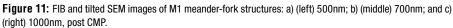

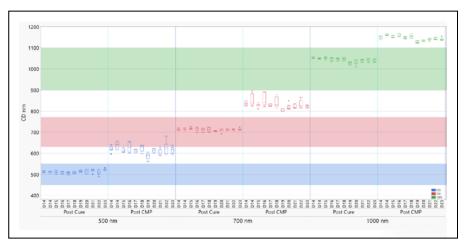

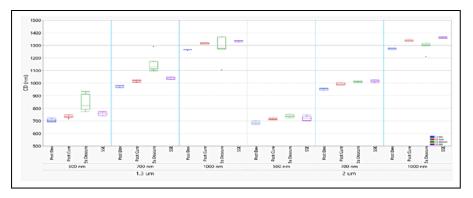

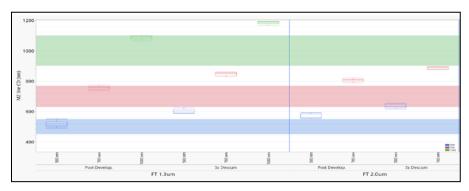

46 Dual-damascene process for a 500nm RDL using a highresolution photosensitive polymer

By Carine Gerets, Eric Beyne, Nelson Pinho, Wen Hung Tseng, Tinneke Paulus, Nouha Labyedh, Gerald Beyer, Andy Miller [imec]

## DEPARTMENTS

#### **INDUSTRY EVENTS**

56 EPTC 2024 – Highlights of the 26th EPTC Conference By Tang Gongyue

[A-Star Institute of Microelectronics]

59 ECTC 2025 – Leading-edge packaging and component breakthroughs pushing the scale of connectivity

By Przemyslaw Gromala [75th ECTC Program Chair]

# Unleash the Future with S-Connect<sup>™</sup> Technology

Amkor's S-Connect technology transforms semiconductor packaging with high-density integration, modular design, and compact form factors.

Ideal for high-performance computing, edge devices, AI, and data centers, S-Connect significantly reduces power consumption, supporting energy-efficient computing and driving sustainable technological advancements.

© 2025 Amkor Technology, Inc. All Rights Reserved.

# Advance the Future with S-SWIFT<sup>™</sup> Technology

Amkor's S-SWIFT™ technology redefines heterogeneous IC packaging. It enables high-performance, cost-effective integration of multiple chiplets and memories.

mkor

This technology increases I/O and circuit density, paving the way for advanced 3D package structures, making it indispensable for next-gen mobile and networking applications.

Follow us @amkortechnology

# Co-packaging of photonic and electronic ICs on glass interposers

By Peter O'Brien, Das Kumar [Tyndall National Institute]

s high-frequency communication, data centers and artificial intelligence

(AI)-driven computing push the limits of existing technology, the need for advanced packaging solutions that efficiently integrate photonic and electronic components has never been greater. While silicon and organic interposers remain widely used, they struggle to meet the thermal and electrical demands of nextgeneration systems. In contrast, glass interposers offer a compelling alternative, delivering low radio-frequency (RF) loss, high thermal stability, and precise microstructuring capabilities—critical factors for high-performance applications.

This article explores the co-packaging of photonic integrated circuits (PICs) and electronic integrated circuits (EICs) using glass interposers, leveraging through-glass vias (TGVs) to enable highspeed RF interconnects. Many of these developments have been achieved within the PhotonicLEAP project, funded by the European Commission under the Horizon Europe research program [1].

Building on advancements in flipchip bonding, laser-assisted packaging, and free-space micro-optics integration [2], we introduce a fully glass-based photonic transceiver package designed for high-frequency applications. For photonic packaging to achieve widespread adoption, it must transition from earlystage research to scalable, cost-efficient manufacturing. This requires standardized design and assembly processes that align PICs, optical components, and packaging substrates. Equally important are advancements in automation and precision assembly, which will reduce costs and enable high-volume production of glassbased photonic systems.

#### Glass as a packaging material

Glass interposers are gaining popularity in IC packaging because of their unique material properties and advantages over traditional silicon and organic interposers. Glass interposers are increasingly recognized for their suitability in radio frequency (RF) and millimeter-wave (mmWave) applications, primarily due to their low loss tangent, which minimizes signal attenuation at high frequencies. This characteristic makes them ideal for advanced communication systems, including 5G and beyond.

Glass benefits from higher thermal stability making it suitable for high-power applications. It has a low coefficient of thermal expansion (CTE) and is comparable to that of silicon ( $\sim 3.2$  ppm/K), thereby reducing thermal stress and warping. Incorporating TGVs into glass substrates significantly enhances local thermal conductivity. While unmodified glass typically exhibits a thermal conductivity around 1.2W/mK, the addition of TGVs can elevate this value to approximately 94W/mK. [3]. Consequently, integrating TGVs into glass interposers is a promising approach for managing thermal challenges in advanced electronic packaging. Furthermore, unlike organic materials, glass provides excellent dimensional stability, and bonding surfaces can be made flat to improve yield without additional fabrication steps.

Unlike silicon wafers, panellevel processing of glass would significantly scale up and reduce cost of manufacturability. In photonics packaging, optical properties of glass provide unique advantages where free space micro-optics and optical waveguides can be seamlessly integrated. Challenges include material brittleness, process maturity of TGVs, and complexity of integration with mainstream semiconductor packaging.

#### **Glass wafer processing using LIDE**

LPKF's laser-induced deep etching (LIDE) technology enables the microstructuring of glass with the fabrication of precise, high-aspect ratio features without introducing defects such as micro-cracks or chipping. This innovative process consists of two key steps:

- Laser modification, where specific regions within the glass substrate are selectively altered according to a predefined pattern.

- 2. The laser-modified areas (from step #1) are removed through a controlled wet chemical etching process, resulting in clean and highly-accurate microstructures.

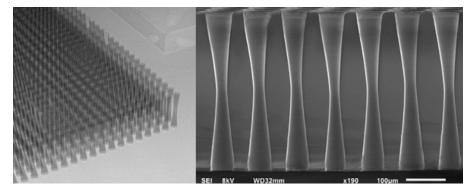

Figure 1 shows the typical microstructured hourglass, or V-shaped vias, in glass using the LIDE process. LIDE technology is compatible with standard silicate-based glasses and can produce features as small as 5µm, with

Figure 1: Hourglass shaped through-glass-via (TGV) using the LIDE process.

aspect ratios reaching 1:50. This makes it highly suitable for applications in semiconductor packaging, microfluidics, and display technology.

The following sections discuss glass wafer specifications and microhole/panel processing associated with using LIDE.

**Glass wafer specifications.** Glass interposers for multiple applications in the same wafer were designed using the LIDE process. BF33 (Schott) glass wafer material with a 200mm diameter and 0.5mm thick was used to fabricate the interposer. The TGVs have an aspect ratio of 1:10.

A standard cavity depth of up to  $(270\pm2)\mu$ m was achieved in the same wafer. The average TGV top and bottom diameters, measured using light microscopy, are calculated to be  $(50, 32\pm0.42)\mu$ m. Additionally, SEM cross-sectional analysis confirms a homogeneous hourglass TGV profile, consistent with the expected LIDE procedure. The average taper angle is  $(1.5\pm0.5)^{\circ}$ .

Micro-hole and panel processing. The minimum via diameter achievable is  $10\mu$ m, with uniform micro-hole diameters across a single substrate. The typical aspect ratio ranges from 1:10, but can reach up to 1:50, depending on the glass type. LIDE-generated micro-holes exhibit smooth, crack-free, chip-free, and stress-free sidewalls, ensuring reliable metallization. The taper angle varies between 0.1° and 30°. V-shaped micro-holes can be formed by restricting etching to a single side of the modified glass. Different via diameters can be

achieved through multiple etching runs.

LIDE technology supports all standard wafer sizes, including 100mm, 150mm, 200mm, 300mm, and 450mm. However, panel formats are limited to dimensions below  $510 \times 510$  mm<sup>2</sup>, and glass thickness is restricted to below 0.9mm.

#### **Glass RDL design rules**

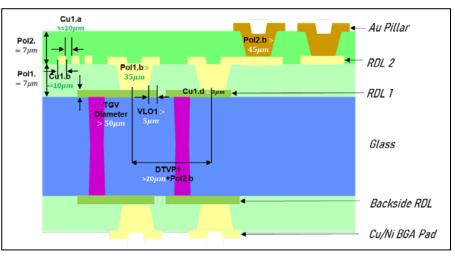

With precisely-structured TGVs and cavities enabled by LIDE, glass wafers can serve as an ideal substrate for redistribution layers (RDLs) in advanced wafer-level packaging (WLP) applications. Figure 2 shows the essential design rules for RDLs in glass for WLP technology. Two RDLs on the top of the glass wafer are passivated by polyimide film.

Bond pads are metallized with Au. The height of the Au pillars can be set between  $1\mu m$  up to  $16\mu m$ , but is fixed throughout a single wafer. The hour-glass TGVs—with a nominal landing diameter of  $50\mu$ m and waist diameter of  $24\mu$ m are filled with copper, and they route the topside RDLs to a single layer of backside RDL. A minimum L/S of  $10\mu$ m applies on all RDLs. The ball grid array (BGA) pads are copper-nickel alloy and can be set to an arbitrary diameter with a minimum distance-to-via-pad (DTVP) of  $20\mu$ m. The minimum via-landing-overhang (VLO) distance is  $5\mu$ m and applies also to vias between RDLs. The minimum via diameter between topside RDLs is  $35\mu$ m.

The following sections discuss various aspects of RDL design rules.

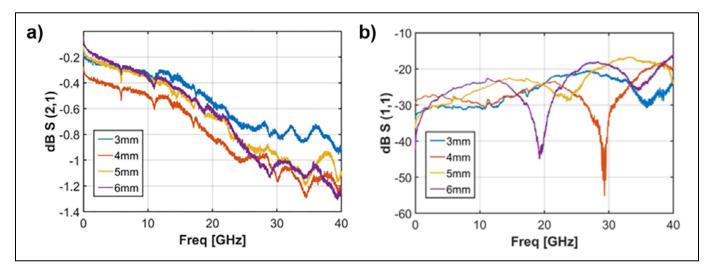

**High-frequency characteristics on glass.** Given the glass fabrication design rules, coplanar ground-signal-ground (GSG) transmission lines were designed and tested. Transmission lines with

Figure 2: Design rules for redistribution layers (RDLs) in glass.

Figure 3: Measured S-parameter results with: a) S21, and b) S11, on GSG transmission lines up to a line length of 6mm on glass RDL 1.

Figure 4: Glass interposer for a flip-chipped InP PIC along with four driver EICs. The package includes a custom microlens for out-of-plane coupling.

lengths of 3mm, 4mm, 5mm, and 6mm with a GSG configuration were fabricated on a glass wafer on RDL1 using design rules; results are shown in Figure 3. Simulation and measurement results of S21 and S11 were performed up to 40GHz and show excellent agreement, thereby validating the electrical parameters later used for the design to support 25GHz transceiver package-level operation.

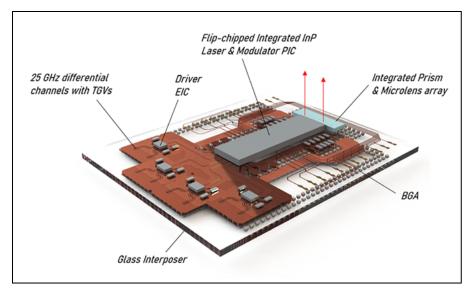

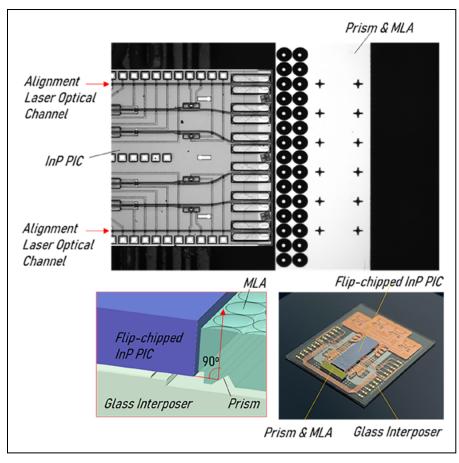

Realized co-packaged transceiver using a glass interposer. Building on the electrical performance of glass-based interposers, a fully-integrated photonicelectronic package was developed to demonstrate the feasibility of high-speed signal transmission on a glass platform. The package incorporates an InP photonic integrated circuit (PIC) with four laser and modulator channels, operating at bandwidths up to 25GHz. These components are driven by differential RF signaling through a dedicated SiGe driver chip, thereby leveraging the highfrequency performance of glass RDLs and TGV interconnects.

The glass interposer design with the InP PIC and co-packaged driver EICs, capacitors, and the microlens array (MLA) is shown in **Figure 4**. The RF input is applied to BGA pins in the glass interposer. One hundred Ohm (i.e., 100 Ohm) differential ground-signal-signal-ground (GSSG) transmission lines were designed using TGVs to provide RF input channels to the driver EICs. The routing is made through the single RDL at the bottom, metallized TGVs, and double RDLs on top of the glass interposer following fabrication design rules.

The co-packaged EIC to PIC RF output channels are routed on the top two RDLs using an edge-coupled microstrip configuration; these lines are 50 Ohm differential GSSG transmission lines. Simulation (not shown here) results of these interconnects between copackaged EICs and the PIC indicate a 1.25dB insertion loss at the 25GHz broadband operational frequency. The return loss is below -20dB per channel. In addition, alignment laser channels were incorporated to facilitate active alignment of the micro-optics on the flip-chipped PIC for out-of-plane coupling. The integrated prism and microlens array (prism and MLA) from FocusLight is constructed from silicon, and a cavity is designed on the glass interposer to house the microlens in the package.

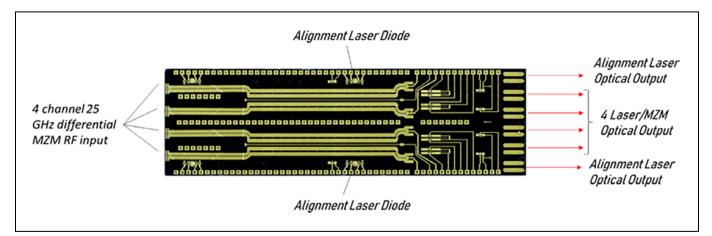

PIC. The InP-based PIC consists of an array of four Mach-Zehnder modulators (MZMs) with an integrated laser source. The distributed feedback (DFB) laser sources are highly efficient, as both ends of a single laser feed into two separate modulators. The RF interface of the capacitively-loaded traveling wave electrode (TWE) of the MZM is positioned on the left side, while the optical interface is on the right, and the DC contacts are routed to the upper and lower sides of the chip. The electro-optical RF response of the modulator was measured up to 67GHz, with an electrical/optical 3dB bandwidth of 40GHz, exhibiting a gradual roll-off.

**Figure 5** shows the InP PIC with two additional channels for the alignment lasers, in addition to the four laser/ MZM channels. The additional channels are dedicated to the active and rapid alignment process of the optical MLA.

Figure 5: A flip-chip compatible InP PIC with integrated two alignment laser diodes, in addition to four laser and MZM channels. A differential signal applied to the MZM RF input enables 25GHz broadband operation in the package.

The four independent MZM channels are integrated with  $2 \times 25$  Ohm RF termination resistors and laser sources each, operating at a wavelength of 1310nm. The measured mode-field diameter (MFD) of the edge coupler is asymmetrical, measuring  $3.7\mu$ m in the x-direction (aligned with the chip's edge) and 2.9µm in the y-direction (vertical).

Driver EIC. The four MZMs of each PIC will be driven by individual driver electronic ICs (EICs). These driver EICs have been designed at FRN-HHI as ultra-low power SiGe 2-bit digital to analog converter (DAC) drivers for low-power high-bandwidth optical transmission systems. The EIC is codesigned and optimized with respect to FRN-HHI's InP-based MZM-modulator regarding impedance matching and signal integrity. By combining a DAC with the linear driver to generate PAM-4 signals for the optical transmission, a cost-efficient and power-saving transmitter for 50 to 100Gbit/s could be realized. The 2-bit DAC driver with chip dimensions of 1050µm x 750µm integrates PAM-4 encoding circuits with an amplification sub-circuit to drive the co-designed MZM with a power consumption of less than 150mW per EIC.

Integrated prism and microlens array. The prism and MLA from FocusLight are designed for out-of-plane coupling of the InP PIC optical I/O. The prism turns the light beam by 90 degrees for the out-of-plane coupling, and the MLA collimates the expanded beam as shown in **Figure 6**. The expansion of the beam allows for the relaxation of the alignment tolerances for the fiber array (FA) connector.

The prism and MLA are constructed from silicon. Fabricating the silicon prism for total internal reflection presents a challenge because the KOH solution selectively etches along the (111) crystalline plane, which is angled at 54.7° relative to the standard (100) dicing face. Standard wafers would result in a beam misalignment with the PIC surface, negating the advantages of a surfacenormal optical connection. To overcome this, the wafer was specially "mis-cut" to bring the etching plane within 1° of the ideal 45°. Simulations indicate that even a 1° deviation could introduce up to 3dB of optical losses, emphasizing the critical nature of this fabrication process.

Additionally, it is crucial to maintain the misalignment between the top and bottom lens features within  $1\mu m$  relative to each other.

The collimating MLA is produced through the deep reactive ion etch (DRIE) method, which ensures a smooth surface that minimizes light scattering. These microlenses are initially formed on a large wafer and later separated using a dicing saw. Additionally, this surface is precisely positioned to maintain the total optical path length from the PIC facet to the lens top, ensuring effective beam collimation.

For an air gap of  $65\mu$ m between the PIC facet and the silicon-integrated prism and MLA, the total optical path through the silicon lens measures  $550\mu$ m, with the wafer itself being  $500\mu$ m thick. The radius of curvature (ROC) of the collimating surface

is designed to expand the beam in the x-direction to  $100\mu$ m—achieved with an ROC of 556 $\mu$ m. This beam size was chosen to align with future standardized optical expanded beam connectors. Due to the source's ellipticity, the expanded beam size in the other direction is  $128\mu$ m, and it remains partially collimated.

Figure 6: Prism and microlens array actively aligned to an InP PIC for out-of-plane coupling.

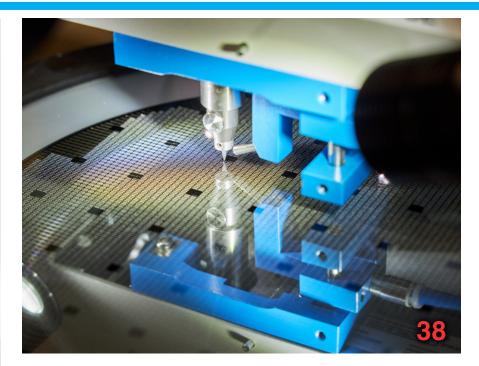

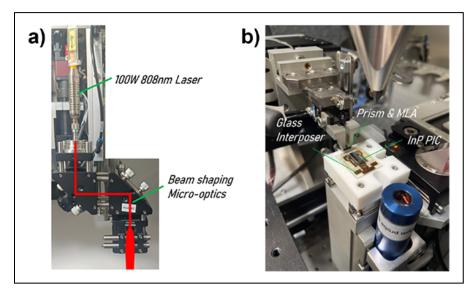

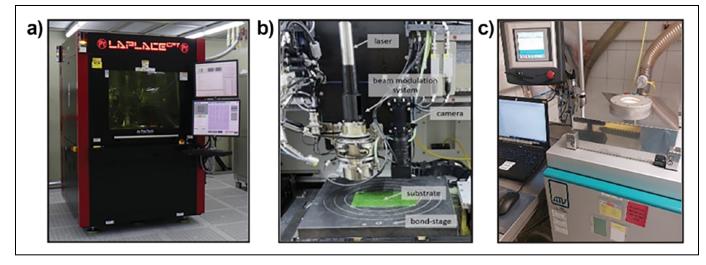

Figure 7: Custom ficonTEC CL1500 for assembly with: a) 100W 808nm laser and beam-shaping optics for flip-chip bonding a PIC to the glass interposer; and b) Active and automated optical setup for the prism and MLA alignment to the PIC.

#### Packaging assembly process

The CUSTOMLINE and FIBERLINE platforms-from ficonTEC [4]-are developed for the accurate flip-chip, laserassisted bonding (LAB) of the EICs and PIC and the accurate alignment of the microoptics on glass interposers, shown in Figure 7. The LAB developed on CL1500 [5] ensures controlled thermal cycles and even heat distribution, thereby enhancing the reliability and performance of components such as laser diodes, photodiodes, micro-optical elements, and lenses. An automated active alignment and attach process of the micro-optics is developed on an F300 platform, where the F300 is tailored for manual or semiautomated MLA pick-ups, closed-loop fastactive alignment, and ultraviolet (UV) epoxy dispensing and curing.

Flip-chip bonding of PIC on glass. A dedicated laser solder reflow system was designed for in-package photonic system integration as shown in Figure 7a. The system utilizes an 808nm laser to bond InP PICs onto glass interposers. Several challenges arose during process development, including handling PICs without obstructing the laser beam, optimizing laser beam shaping, and maintaining precise temperature control. A transparent vacuum pick-up tool (PUT) was developed to apply a uniform downward force during reflow without interfering with the laser.

**Micro-optics assembly. Figure 7b** shows the setup for active alignment of the flipchipped PIC to the prism and MLA. The glass interposer was designed so that both the alignment laser diodes of the PIC can be powered up using probe needles, and the prism and MLA placed on top of the glass cavity and actively aligned.

The observed coupling losses range from 1.4 to 1.75dB [6]. These losses can be further reduced through improved mode matching and refinements in the microlens fabrication process. Due to beam collimation, the alignment tolerance of the FA connector increases by approximately 35 times, reaching about 28µm, with a slight discrepancy between beam axes caused by the ellipticity of the couplers.

#### Summary

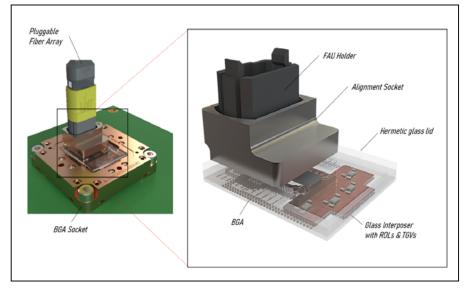

We highlighted our ongoing progress in co-packaging flip-chipped EICs and PICs, where the assembled components, as well as the equipment, were simultaneously custom designed. Standardized design rules spawning from this work will contribute to scaling up and lowering cost of photonics

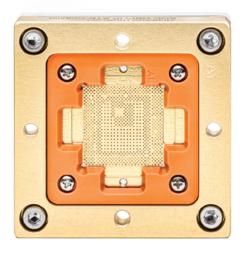

Figure 8: All-glass package with capping lid and socket for a pluggable FA connector, inserted into a BGA socket for an end-user application.

packaging, making it viable for wider industry adoption.

To prepare for the end-user setup, the final package will feature a custom AR-coated capping lid and a 12-channel MPO pluggable fiber connector from SENKO, as illustrated schematically in **Figure 8**. The all-glass package will be electrically-powered through a JohnsTech BGA socket, designed for a 32  $\times$  40 array of BGA pins with high-frequency spring-loaded probes. A standard BGA bond pad pitch of 0.5mm has been utilized.

The size of the glass interposer has been standardized to accommodate multiple package types with varying applications on the same glass wafer. For example, in addition to the telecommunications package layout discussed here, the same 200mm glass wafer can also include a glass interposer layout for a biomedical application.

TGVs facilitate both direct current (DC) and RF electrical routing to the BGA beneath the interposer. Standardization enables wafer-level handling by testing and assembly equipment, which is essential for scaling up photonics packaging.

Glass interposers are a promising alternative to silicon and organic substrates for high-frequency applications, photonics packaging, and wider adoption in the semiconductor industry. While challenges such as brittleness and process maturity exist, glass technologies are enabling precise micro-structuring, via formation and high-frequency/high-density electrical interconnects making glass-based interposers increasingly viable in advanced photonic packaging solutions.

#### **Acknowledgements**

We would like to acknowledge the technical support from our PhotonicLEAP project research partners including, Fraunhofer IZM and HHI, LPKF Laser & Electronics SE, FocusLight Technologies Inc., ficonTEC GmbH, Bosch GmbH, imec, and Technical University of Eindhoven.

#### References

- 3. European Commission, Photonic Wafer-Level Integration Packaging and Test (H2020-101016738), Horizon 2020, [Online]. Available: https://cordis.europa.eu/project/ id/101016738. [Accessed: Feb. 28, 2025].

- D. S. Kumar, P. O'Brien, K. Kröhnert, N. Schöning, M. Schulz-Ruthenberg, N. Ambrosius, et al., "Design of BGA style glass interposer for 2.5D integration of photonic ICs," IEEE Photonics Conf., Rome, 2024.

- K. Kröhnert, M. Wöhrmann, M. Schiffer, C. Kelb, N. Ambrosius, P. Gupta, et al., "High aspect ratio through-glass vias as heat conductive element," IMAPS Nordic Conf. on Microelectronics Packaging (NordPac), Gothenburg, Sweden, 2022.

- 6. ficonTEC, "Advanced assembly solutions for photonics," https://www. ficontec.com/wp-content/uploads/ pdf/en/A-2501-v1-web.pdf. [Accessed 25 Feb. 2025].

- K. Shortiss, H. Y. Hwang, J. Parra-Cetina, M. Seyfried, P. O'Brien, "Development of 808nm laserassisted-bonding (LAB) for photonic system-in-package integration," Conf. on Lasers and Electro-Optics Pacific Rim (CLEO-PR), Tech. Digest Series (Optica Publishing Group, 2024).

- K. Gradkowski, H.-C. Wang, D. S. Kumar, W. Noell, K.-O. Velthaus, P. O'Brien, et al., "Recent advances in fiber-to-PIC packaging technologies for scalable manufacturing," SPIE Photonics West, San Francisco, CA, USA, 2025.

#### **Biographies**

Prof. Peter O'Brien is head of the Photonics Packaging & Systems Integration Group at the Tyndall Institute, University College Cork, Ireland. Prof. O'Brien previously founded and was CEO of a start-up company manufacturing specialty photonic systems for biomedical applications, which he sold in 2009. Before this, he was a researcher at the California Institute of Technology and at NASA's Jet Propulsion Laboratory, where he was involved in developing sub-millimeter wave devices for remote sensing applications. He received his degree and PhD in Physics from Trinity College Dublin and U. College Cork. Email: peter.obrien@tyndall.ie

Das Kumar is a Senior Researcher at Tyndall National Institute, University College Cork, Ireland. He finished his PhD in EEE from U. of Nottingham, UK and specializes in advanced photonic packaging technologies like glass interposers, for high-speed and high-density electrical and optical interconnects. In his former role, he developed waveguides in glass using ultrafast laser inscription technology. At Tyndall, he manages PhotonicLEAP and leads design of RF packages for photonic applications. Email das.kumar@tyndall.ie

# Measuring the Invisible XM8000<sup>™</sup>

Automated X-ray Metrology

## Advance your Semiconductor X-ray Metrology with XM8000™

Nordson's XM8000<sup>™</sup> AXM system provides industry-leading measurement of micron-scale features in wafer and panel level advanced packaging applications.

- Using proprietary imaging chain including Nordson's own design X-ray tube and CMOS detectors to generate ultra-high resolution images capable of detecting and measuring hidden defects within complex semiconductor packages.

- Successfully being used to enhance packaging quality in a variety of applications including bump voiding, TSV/TGV measurement, fill analysis and chip gap height measurement.

Count on the XM8000 to improve your semiconductor advanced packaging yields, processes and productivity.

# A New Spin on Inspection SpinSAM<sup>™</sup>

**Acoustic Inspection**

## The SpinSAM<sup>™</sup> automated inspection system delivers industryleading throughput with unparalleled sensitivity for accurately locating defects in wafer based assemblies.

The SpinSAM's innovative spin scanning method efficiently and accurately scans up to 4 (300mm) wafers simultaneously, at 41 wafers per hour with best-in-class defect capture and image quality. With 4 matched waterfall transducers, the SpinSAM was meticulously engineered to attain full wafer scans in less than 6 minutes.

Ideal applications include bonded wafers, Chip-on-Wafer, stacked wafers, MEMS, over-molded wafers and more.

# Impact of BGA solder metallurgy on BLR failure modes in flip-chip packaging

By Jaimal Williamson, Yutaka Suzuki [Texas Instruments]

ith the global proliferation of highcomputing systems

driving trillion operations per second to support advanced driver assistance systems (ADAS) applications, enhancing the semiconductor packaging reliability margin is a quintessential responsibility for packaging engineers. The initiative to establish a continuous-improvement mindset befitting an automotive target of zero defects requires a deep understanding of material science principles that includes the chemical structure and material property relationships of organic packaging materials and the strain-rate-dependent viscoplastic properties of solder materials.

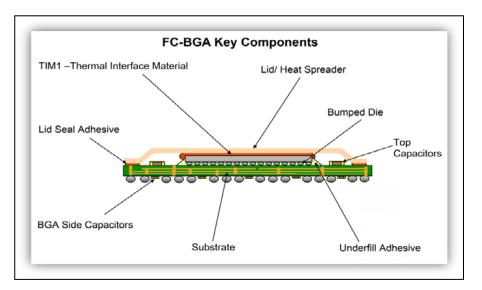

Flip-chip ball grid array (FCBGA) packages are becoming analogous to "servers on wheels," as advanced design rules (i.e., a tighter bump pitch at the first-level interconnect, finer substrate lines and spaces, higher power densities) continue to be trends necessitating highdensity interconnect routing. Figure 1 illustrates a FCBGA package supporting a myriad of high-end applications. As a result, chip-to-package interaction becomes more challenging, as the implementation of advanced design rules drives specific packaging features such as a reduced cross-sectional area of copper lines, a thinner substrate core, and a higher degree of warpage, which can be exacerbated under Automotive Electronics Council-Q100 reliability conditions [1]. In this article, we'll discuss a board-level reliability (BLR) study of two common lead (Pb)-free alloys as the BGA solder ball in flip-chip packages. These Pb-free alloys are denoted as alloy A and alloy B. Alloy A is bismuth free, whereas alloy B contains less than 5% bismuth.

Bismuth-contained solders are wellknown for having higher fracture toughness, which is expected to show higher mechanical reliability under the temperature cycling test. The fundamental mechanical behavior of bismuth-contained solders is prone to other mechanical failure risks, however. Failure modes include copper (Cu) metal pad and trace cracking, and buildup passivation film cracking. We also discuss the methodologies to assess expected failure modes of two different alloys undergoing reliability tests, using a combination of finite-element-analysis (FEA)-based thermomechanical modeling and empirical test results. FEA-based thermomechanical models reflecting strain-rate dependent viscoplastic material represented by the Anand model, combining the image processing technique, and failure analysis reports, enabled the details to be reflected for a deep understanding of root causes.

Understanding failure modes under dynamic temperature extremes requires a methodical approach to discover the root cause. For example, at the material characterization stage, the packaging engineer should be conscientious when preparing samples for characterization, as fluctuations in geometric dimensions caused by imperfections (nonuniformity, voids) can have detrimental effects. Sample imperfections can affect the accuracy of material property measurements and cause erroneous values during stress modeling simulations. Characterizing granular details, such as each of the materials that make up the composite FCBGA substrate, is prudent because implementing time-dependent deformation and viscoelastic properties of the organic material set are critical for reliable stress-modeling predictions. This methodology is essential to facilitate the best opportunity for predicting the onset of failure and maximum stress.

As packaging designs become more complex, with demand for 2.5D and 3D multi-chip modules increasing, one result is the significant role that warpage plays because out-of-plane displacement can become a dominant influence to failure modes caused by tensile stresses. Modulus and coefficient of thermal expansion (CTE) are two thermomechanical factors used to decide the bill-of-materials for flip-chip packaging reliability. Because of the anisotropic behavior [2] of certain polymeric materials in the composite substrate, CTE can vary two to three times in the z-direction compared to the

Figure 1: Representative FCBGA package.

# BALL PLACEMENT & LASER SOLDERING

x and y directions. The orientation of polymer chains in the x and y directions can differ significantly in the z direction, which can be compounded by filler or glass reinforcement.

In addition to the considerations above, flip-chip assembly process conditions involving multiple Pb-free reflow temperatures and elevated static heat exposure, such as underfill and lid attach curing conditions, are imperative variables to elucidate the impact of package stresses caused by chemical shrinkage during heating and cooling. As underfill adheres to the die and substrate (as illustrated in **Figure 1**), understanding the batch-to-batch differences as variations in formulation can affect cure stress as a function of the molecular weight distribution. The bottom line is a holistic approach examining the core fundamentals spanning the characterization of neat and composite

substrate materials, assembly processes, and environmental conditions to validate stress modeling against empirical findings.

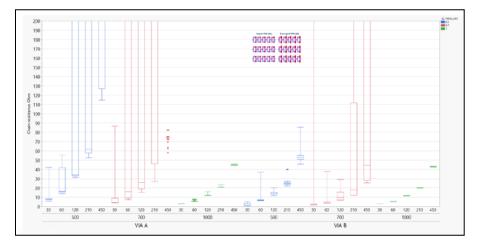

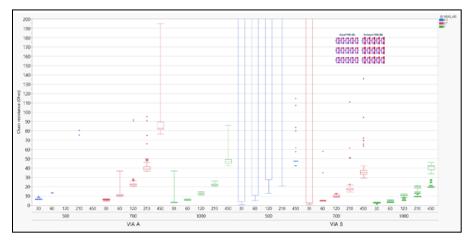

#### BLR impact based on BGA alloy material properties

Automotive devices must meet one of the highest reliability standards in the industry. Documenting lessons learned forms a basis for continuous improvements. As such, maximizing BLR findings were studied as a continuous improvement initiative, with a specific focus on studying an alloy with higher modulus and tensile strength. Throughout this article, we will describe the aforementioned alloy as alloy B, and compare it to the incumbent alloy, denoted as alloy A. **Table 1** shows a normalized view of the material properties between alloy A and alloy B.

| Material property      | Alloy A | Alloy B |

|------------------------|---------|---------|

| Young Modulus (GPa)    | 1       | 1.45    |

| CTE (ppm / C)          | 1       | 0.94    |

| Tensile strength (MPa) | 1       | 3.1     |

| Elongation (%)         | 1       | 1.37    |

**Table 1:** Normalized view of the material propertiesbetween alloy A and alloy B.

The comparison between alloy A and alloy B shows the difference in material properties. Alloy B has an approximately 30% higher modulus and elongation than alloy A. In addition, the tensile strength of alloy B is three times that of alloy A. We hypothesize that this disparity in material properties is the reason that different failure modes manifest during BLR.

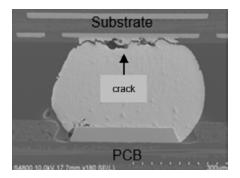

During BLR testing, the expected failure mode of the second-level interconnect is bulk solder cracking. Figure 2 illustrates bulk solder cracking

Figure 2: Illustration of bulk solder cracking, with a crack observed on the package side.

| Leg  | Package type | Body size (mm x mm)         | Substrate material set                   |

|------|--------------|-----------------------------|------------------------------------------|

| TV 1 | FCBGA        | greater than 30mm on a side | HVM material set (ABF as dielectric)     |

| TV 2 | FCBGA        | greater than 30mm on a side | HVM material set (ABF as dielectric)     |

| TV3  | FCCSP        | less than 15mm on a side    | HVM material set (prepreg as dielectric) |

| TV4  | FCCSP        | less than 15mm on a side    | HVM material set (prepreg as dielectric) |

Table 2: Description of FCCSP and FCBGA packaging types evaluated during BLR.

typically caused by solder fatigue during the temperature cycling test. Temperature cycling conditions (condition G, soak mode 2), as based on Joint Electron Device Engineering Council JESD22-A104 [3], serve as the basis for the hot and cold temperature delta analyzed during stress modeling. Maximizing the cycles to first failure during the condition G temperature cycle is the focus of our continuous improvement initiative.

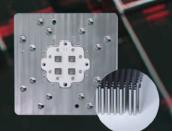

In this study, we subjected two lidded FCBGA packages (see Figure 1) to BLR testing based on JESD22-A104. The only difference was assembling the parts with alloy A and alloy B. In addition, we subjected two overmolded flip-chip chipscale packages (FCCSPs) to BLR testing, again assembling the devices with alloy A and alloy B. Figure 3 is a representative image of the FCCSP evaluated during this study. Table 2 lists the attributes of the FCCSP and FCBGA packages. The first cycles to failure and Weibull analysis (not reported) demonstrated high margin as device requirements were exceeded. However, the failure mode for devices

Figure 3: A representative FCCSP.

assembled with alloy A and alloy B showed divergent failure mechanisms.

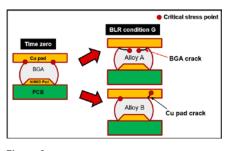

#### Hypothesis of failure mode during BLR testing

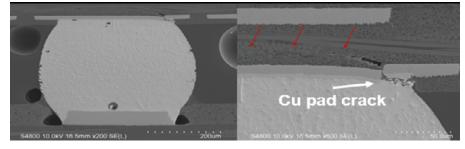

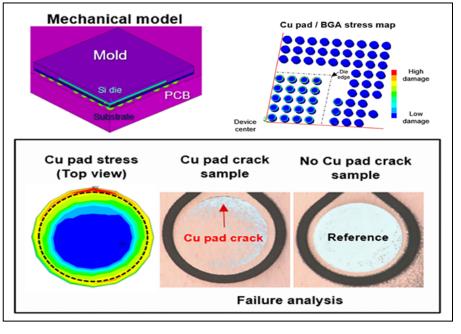

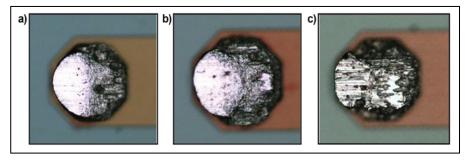

As stated previously, bulk solder cracking is the preferred failure mode. This failure mode is consistent with the solder fatigue of alloy A, as illustrated in **Figure 2**. In contrast, alloy B exhibited a different failure mode that occurred at the BGA pad – that is not in the bulk solder. With both the FCCSP and FCBGA package types, the BGA Cu pad cracking at the solder mask opening was the onset of failure during BLR testing.

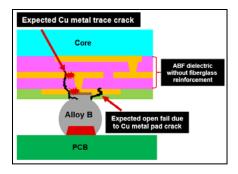

**Figure 4** shows an example of the FCCSP failure mode at first cycles to failure, which far exceeded the device requirements. Similarly, the onset of failure for the FCBGA package having a more compliant Ajinomoto buildup film (ABF) dielectric material than the fiber-

reinforced prepreg dielectric material used for the FCCSP device, also failed at the BGA Cu pad.

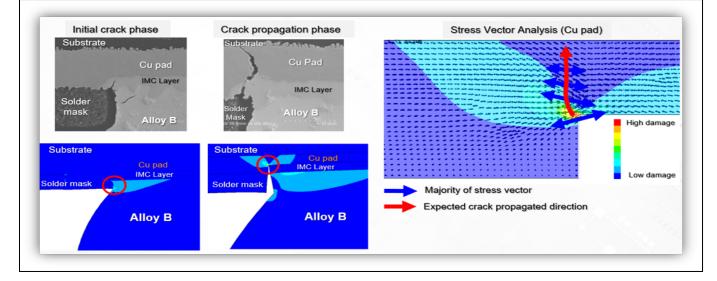

The modulus and CTE of the ABF dielectric are approximately 6 times and 11 times lower, respectively, than the fiber-reinforced prepreg dielectric material. Because of the disparity in material properties, the vector of the crack propagation path between the FCCSP and FCBGA package presented an observable difference. Figure 5 shows the onset of failure in the FCBGA package as assembled with alloy B.

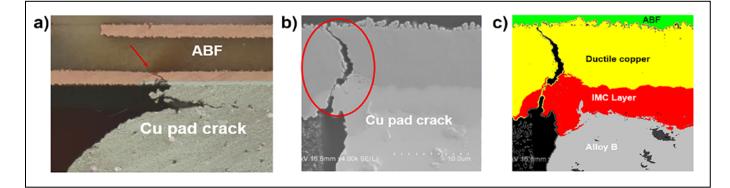

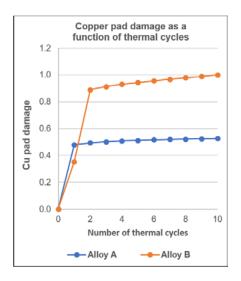

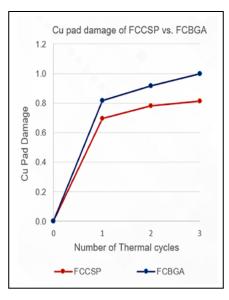

As previously mentioned, the failure mode between the FCCSP and FCBGA packages exhibited divergent crack propagation paths. Our hypothesis is that the failure mode develops as illustrated in Figure 6. Based on Table 1, because alloy B shows a higher fracture strain energy than alloy A, the thermal stress in the Cu pad is expected to accumulate without solder cracking under the temperature cycling test. The thermomechanical models shown in Figure 7 estimate the Cu pad crack risk between the two alloys-assuming that the solder cracking issue does not occur. From the chart, you can see that alloy A has a lower Cu pad crack risk than alloy B after the second cycle. In

Figure 4: Onset of failure with FCCSP during BLR with alloy B.

Figure 5: Onset of failure in a FCBGA package during BLR with alloy B: a) A low-magnification optical micrograph; b) A higher magnification scanning electron microscopy image (SEM); and c) Delineation of alloy B, intermetallic compound (IMC) layer, ductile BGA Cu pad and the underlying ABF material.

addition, alloy A is expected to generate bulk solder cracking as a major failure mode given its inherently lower fracture strain energy (lower than alloy B).

As for alloy B, if the accumulated strain energy in the Cu pad exceeds

**Figure 6:** Hypothesis of the failure mode between alloy A and alloy B.

**Figure 7:** Cu pad damage between alloy A and alloy B as a function of the temperature cycle.

the fracture toughness, a Cu pad crack would occur. This is confirmed from the stress contour map of the Cu pad shown in **Figure 8**. The critical stress point is almost consistent with the actual Cu pad location from the failure analysis. Because the crack propagation rate through the IMC layer is expected to manifest faster than ductile materials, the crack propagated immediately through the IMC layer. The stress concentration region should move to the tip of the crack. **Figure 9** shows the thermomechanical model with stress vector analysis to estimate the crack

propagation direction. The critical stress points and propagation direction of the crack using the thermomechanical models are almost consistent with the empirical test result.

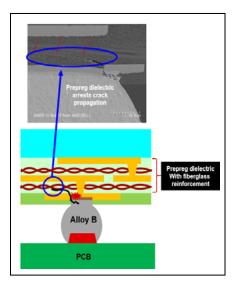

In the FCBGA package, the crack propagation vector follows a more upward path, with the crack trajectory traversing the Cu pad and underlying ABF material, and meandering toward the Cu layer above the bottommost Cu layer in the substrate. In contrast, the FCCSP offers a higher degree of rigidity with the fiber-reinforced prepreg in that it drives more of a

Figure 8: An example of the thermomechanical modeling result for the Cu pad crack risk.

Figure 9: Stress contour map of plastic strain energy for the ductile materials: a) Crack initiation phase; b) Crack propagation phase; and c) Stress vector analysis of the Cu pad.

**Figure 10:** Crack propagation path for the FCBGA package with alloy B.

Figure 11: Crack propagation path for FCCSP with alloy B.

meandering crack propagation path laterally throughout the prepreg dielectric material. **Figures 10** and **11** demonstrate the vector of the crack propagation path between the FCBGA package and FCCSP, respectively. As the figures show, the crack propagation path penetrates more in the FCBGA package because of the difference

**Figure 12:** Comparison of Cu pad damage with the FCBGA package and FCCSP.

in material properties between ABF and prepreg dielectric materials. In Figure 11, the fiberglass reinforcement provides a means to arrest the crack propagation. Figure 12 compares the Cu pad damage between the FCCSP and FCBGA package.

#### Summary

Instilling materials science and engineering principles to establish a fundamental approach to understanding flip-chip packaging failures is a cornerstone to problem solving. We used an FEA-based thermomechanical modeling approach to study the varying failure mechanisms during BLR testing of FCCSP and FCBGA packages assembled with two different Pb-free alloys. The output of BLR testing compared the performance of both flipchip packaging types assembled with alloy B, which had a higher tensile strength and modulus than alloy A. Alloy B initiated a crack propagation failure mode emanating at the BGA Cu pad during BLR testing.

Thermomechanical models of the critical stress points and crack propagated direction were consistent with empirical test results as validated by failure analysis. The material composition of the dielectric material used in the FCCSP and FCBGA packages played a significant role in the magnitude of the crack propagation vector. A higher degree of damage at the Cu pad was found in the FCBGA package (compared to FCCSP) because the ABF-based dielectric without fiberglass reinforcement limited arrest of the crack propagation.

The synergistic use of FEA stress modeling coupled with best failure analysis practices to corroborate failure modes and crack propagation paths helped drive a continuous improvement mentality for the optimal selection of packaging materials. This is paramount to establishing a zerodefect mindset for automotive devices.

#### References

- 1. AEC-Q100 rev J document.

- J. Coburn, et al., "Structure Development in Polyimide Films," Materials Research Society, 1993

- 3. EDEC Standard Temperature Cycling, JESD22-A104F.01

#### **Biographies**

Jaimal Williamson is a Packaging Engineer and Senior Member Technical Staff within Texas Instruments' Worldwide Semiconductor Packaging group, Dallas, TX. His focal areas as a lead technologist include flipchip platform development of advanced CMOS Si nodes, qualification, and productization to support multiple automotive, industrial, aerospace, and defense applications. He has authored and co-authored 30+ journal articles, conference papers, and technical magazine articles, as well as 25+ U.S. patents in the field of semiconductor packaging. He received a BS in Chemistry from Grambling State U. and a MS in Polymers (via School of Materials Science and Engineering) from the Georgia Institute of Technology. Email: jaimal.williamson@gmail.com

Yutaka Suzuki is a Packaging Engineer and Member Group Technical Staff within Texas Instruments' Worldwide Semiconductor Packaging group, Dallas, TX. He specializes in leading the mitigation of mechanical reliability for advanced IC packaging and systems and in developing Multiphysics system co-design simulation and modeling methodology. He has published over 20 papers and technical magazine articles as an author and co-author in peer-reviewed IEEE conferences and JSME. He is an IEEE and IEEE EPS Dallas Chapter member (Region 5).

Elastic Part Recyclable Pogo Socket

TSE Co., Ltd | www.tse21.com | salesap@tse21.com

# Column Replaceable Elastomer Socket

TSE Co., Ltd | www.tse21.com | salesap@tse21.com

# WinWay

🔀 sales@winwayglobal.com

- +886 7 361 0999 / +886 3 656 8282

- www.winwayglobal.com

## Your Trusted Partner in Semiconductor Testing

#### **Vertical Probe Card**

Minimum pitch : 75 um High pin count ≤ 35,000pins

## Spring Probe In-house manufacturing

**Coaxial Socket**

SerDes 224Gbps PAM4 Supports up to 30,000 pins

### **Optical Socket**

SerDes 224Gbps PAM4 Optical alignment

Total Solution for Advanced Semiconductor Test

Functional Burn-in

High Power 1000W High Speed PCIE Gen5 32Gbps

### **Thermal Product**

2000W cooling capacity Temperature : 20 to 150°C

# Reliability challenge of underfills in large-size heterogeneous integration FO-MCM packaging

By Liang-Yih Hung, Chia-Wei Chang, Wen-Yu Teng, Andrew Kang, Yu-Po Wang [Siliconware Precision Industries Co., Ltd]

an-out multi-chip module (FO-MCM) technology has made it possible to integrate a significant quantity of chips and high-bandwidth memory (HBM) devices into a single package with excellent signal and power integrity. These modules address the market drivers of improved computing performance, memory capacity and bandwidth. However, FO-MCM reliability performance is impacted by the increase in bending stress caused by increased warpage as a result of the much larger package size.

Though underfill material is rather conventional, it plays an important role in a large FO-MCM package. Underfill is a composite material that mainly comprises epoxy polymer and silica (SiO<sub>2</sub>) and anti-bleeding agents; adhesive promoters and carbon black dyes are often added to its formulation. Usually, the underfill is dispensed through capillary action to fill the gap between the silicon chip/chip module and an organic redistribution layer (RDL) interposer/substrate to offer physical protection of  $\mu$ bumps/C4 bumps, and acts as a buffer to absorb the stress from coefficient of thermal expansion (CTE) mismatching between the silicon die/chip module and their own carriers.

In this article, the mechanical property and stress strength of a heterogeneous integration fan-out multi-chip module (HI-FOMCM) are investigated. The test vehicle comprises one HI-FOMCM, which is bonded onto an organic substrate. The floor plan of the HI-FOMCM device contained one silicon chip and four HBMs. We used a thermal mechanical analyzer (TMA) and a dynamic mechanical analyzer (DMA) to study the underfill and provide the parameters needed for the models used in the finite element analysis (FEA). The purpose of the FEA is to simulate effects of the glass transition temperature (Tg) and the CTE of the applied underfill on both the warpage of the HI-FOMCM and the corresponding bending stress on the HBM chip. Design of experiments (DoEs) were planned with the studied underfill and validated for MSL3, unbiased highly-accelerated stress testing (uHAST), temperature cycling testing (TCT) and hightemperature storage life (HTSL) testing to discuss the relationship among the reliability results, simulation data, and material properties of the underfills. Moreover, stress-strain curves of the underfill were measured and analyzed to determine the key performance metrics of the HI-FOMCM underfill.

#### Introduction

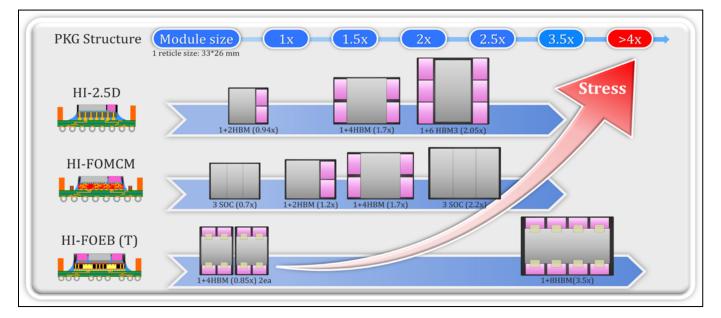

The global data center and autonomous vehicles markets are experiencing rapid growth, driven by the increasing demand for high-performance computing (HPC) to support artificial intelligence (AI) workloads. The AI market is projected to grow at an annual rate of nearly 30% from 2025 to 2030. Heterogeneous integration has emerged as a pivotal trend in advancing AI applications by integrating multiple components, such as AI accelerators (graphics processing units [GPUs], tensor processing units [TPUs], application-specific integrated circuits [ASICs]), HBMs, and I/O controllers into a single package. This approach enables high interconnect density and reduces power loss. The evolution of SPIL's advanced packaging modules' size is illustrated in **Figure 1**. Compared to

Figure 1: The evolution of the size of advanced packaging modules.

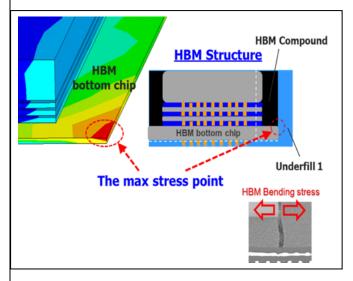

2.5D integration, HI-FOMCMs are more cost-effective, utilizing a RDL instead of a silicon interposer for die-to-die interconnections. However, as the package size increases, thermomechanical stress also rises. For 2.5D integration packages that use a high-stiffness silicon interposer, the bending stress typically occurs at the outer edge of the HBM chip. In contrast, for HI-MCM packages that adopt an organic interposer (RDL), the bending stress is concentrated in the middle region between the ASIC chip and the HBM chip.

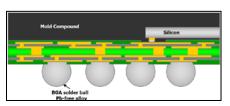

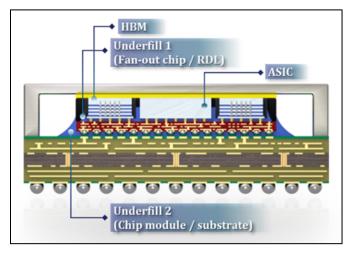

HI-FOMCM packages require the use of underfill materials to protect fragile silicon chips (or chip modules) and copper pillar bumps, or solder bumps, while controlling warpage of the package. Figure 2 illustrates two applications of underfill material in HI-

Figure 2: Schematic of a flip-chip-ball grid array with the heterogeneous integration of a fan-out multi-chip module.

FOMCM packages: Underfill 1 is used to fill the gap between the HBM/ASIC and the RDL, while Underfill 2 is used to fill the gap between a chip modulus and substrate in a fan-out multi-chip module. The primary functions of underfill are as follows:

- 1. To mitigate mismatches in the CTE between silicon chips and their carrier or substrate;

- 2. To enhance resistance to thermal stress;

- 3. To protect against physical stress caused by mechanical shocks, drops, and vibrations;

- 4. To protect against moisture, ionic residues, and unwanted substances; and

5. To promote the adhesion of a component to a carrier or substrate.

However, thermal stress and modulus-related stress between a chip and its RDL on HI-FOMCM packages remain problematic. Therefore, this article shares SPIL's experience in selecting the appropriate Underfill 1 for the HI-FOMCM package.

#### **Evaluation of underfill material**

The following sections discuss underfill selection, the HI-FOMCM test vehicle, and the reliability test conditions.

Underfill selection. The material mechanical properties of UF-01, UF-02, and UF-03 are summarized in Table 1. The measurement data were analyzed using an ANSYS static structural module (a three-dimensional (3D) finite element analysis model) to assess stress and warpage. UF-01, a commonly used underfill material in the fabrication of HI-FOMCMs, was validated in this study by applying it as Underfill 1. Simulation results indicated that reducing the material modulus decreases both the warpage and the HBM chip bending stress in the chip module. The simulation results of the warpage and bending stress are shown in Table 2. The chip module containing UF-01 exhibited the highest HBM chip bending stress and warpage at high temperature. Consequently, two underfill materials with lower bending stress than UF-01, namely UF-02 and UF-03, were selected for evaluation. These materials were examined by SPIL Material LAB, which ensured that the fabricated test pieces were identical and

| Mechanical properties |                     | Underfill type |            |           |

|-----------------------|---------------------|----------------|------------|-----------|

| Item                  | unit                | UF-01(POR)     | UF-02      | UF-03     |

| CTE 1 / 2             | ppm/ <sup>0</sup> C | 38 / 82        | 50 / 100   | 45 / 115  |

| Tg (by DMA)           | <sup>0</sup> C      | 217            | 123        | 169       |

| Modulus RT / HT       | Gpa                 | 6.1 / 1.8      | 5.2 / 0.08 | 5.4 / 0.4 |

| Adhesion on Chip      | Kg                  | 12             | 21         | 14        |

| Adhesion on EMC       | Kg                  | 15             | 16         | 15        |

#### Table 1: Underfill mechanical properties.

| UF Type                         |    | UF-01(POR) | UF-02  | UF-03  |

|---------------------------------|----|------------|--------|--------|

| HBM bending stress              | -  | 1X         | 0.68X  | 0.77X  |

| Chip module<br>warpage at RT/HT | μm | 286/101    | 274/77 | 281/89 |

Table 2: Simulation results with respect to stress and warpage.

| Analysis item    | СТЕ                       | CTE Modulus            |                                   | S.S.Curve        |

|------------------|---------------------------|------------------------|-----------------------------------|------------------|

| Equipment        | TMA                       | DMA                    | Shear Tester                      | UTM              |

| Mode             | Expansion                 | Dual cantilever        | Pudding shear test                | Tensile test     |

| Sample dimension | 6.5*6.5*15mm <sup>3</sup> | 60*10*2mm <sup>3</sup> | Dia. * height: 4*3mm <sup>2</sup> | ASTM D638 type 1 |

| Temperature      | 25~260°C                  | 25~260°C               | 25°C                              | 25°C             |

| Note             |                           |                        |                                   |                  |

Table 3: Equipment used for underfill property measurements.

that all measurement parameters were consistent to maintain accuracy. The dimensions of the test piece and parameters of the measurement platform are listed in Table 3.

The CTEs and storage modulus of the underfill materials were measured using a TMA and DMA, respectively. Adhesion strength between the underfill and chip/epoxy molding compound (EMC) were evaluated using a Dage 4000 Bondtester. The underfill was applied in a pudding mold shape over the surface of the chip/EMC. After curing, the underfill was sheared at a height of  $20\mu$ m to obtain its adhesion strength. To measure the stress-strain behavior, samples were prepared following ASTM D638 (Type 1 dimensions) and tested using a universal testing machine (UTM).

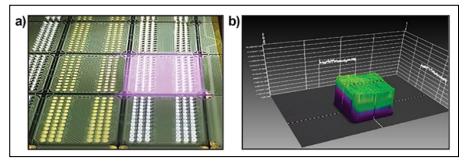

**HI-FOMCM test vehicle.** The selected underfill materials were evaluated in a test vehicle comprising a HI-FOMCM. The test vehicle is shown in **Table 4**. The test vehicle contained a 72.5mm  $\times$  70mm package that bonded with a 45mm  $\times$  30mm HI chip module (1 chip + 4 HBM modules). The fan-out multi-

| Package Structure |                 | HI-FOMCM (I Chip + 4 HBM) |  |

|-------------------|-----------------|---------------------------|--|

| Package size      | $\mathrm{mm}^2$ | 72.5 x 70                 |  |

| Chip module size  | $\rm mm^2$      | 45 x 30                   |  |

| ASIC size         | mm <sup>2</sup> | 28 x 24                   |  |

| HBM size          | mm <sup>2</sup> | 8 x 12 (4 pcs)            |  |

| RDL Layer         | -               | 3L                        |  |

| Substrate layer   | -               | 18L                       |  |

| Heat sink type    | -               | Stiffener ring            |  |

Table 4: Information on the package selected for evaluation.

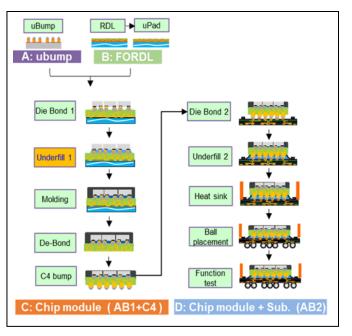

chip module was flipped and bonded to the substrate. The HI-FOMCM fabrication process is illustrated in **Figure 3**. We employed a chip-last process, which was initiated by stacking three RDLs on the wafer surface. Subsequently, one chip and four HBM modules were assembled onto the wafer. The space beneath the fan-out chip was then filled with an underfill (Underfill 1); this underfill was later subjected to examination. Next, a liquid molding compound was applied in a compression molding process to protect the chip module, which was then combined with a substrate, and another underfill (Underfill 2) was used to fill the space between the chip module and substrate. Additional steps were then performed to complete the fabrication of the HI-FOMCM.

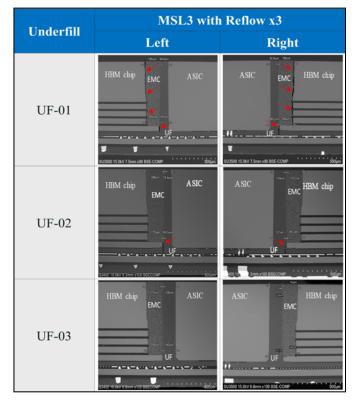

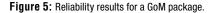

**Reliability test condition.** This study also conducted several experiments to evaluate the performance of selected underfill materials. The testing conditions were as follows: JEDEC Level 3 preconditioning (moisture sensitivity level of 3, 30°C with a relative humidity of 60% for 192 hours) with three reflows at 245°C; 700 cycles of (TCT) under condition B (-55 to 125°C); 96 hours of uHAST at 130°C with a relative humidity of 85% after preconditioning; and 1000 hours of HTSL at 150°C. After the aforementioned reliability tests, scanning electron microscopy

Figure 3: HI-FOMCM fabrication process.

(SEM) was employed to examine the cross section of the HI-FOMCM for any structural damage caused by bending stress.

#### **Underfill materials verification results**

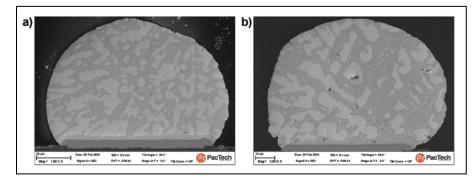

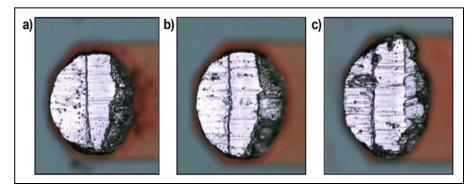

SEM images of the cross sections of the chip modules subjected to MSL3 tests containing UF-01, UF-02 and UF-03 are presented in **Figure 4**. The SEM images of UF-01 revealed cracks originating from the bottom underfill region

Figure 4: SEM image of a cross section after the MSL3 test.

and propagating to the sides and top of the HBM chip. To investigate the root cause of these cracks, an ANSYS 3D finite element analysis was conducted. The stress contour simulations revealed that the maximum stress points were concentrated at the corner of the HBM chip, as illustrated in Figure 5.

Figure 5: Contour of a weak point at a corner of a HBM chip.

SEM images of UF-02 shows the cracks in the chip module extended only from the corner of the HBM chip toward the bottom underfill area—the cracks did not extend upward to the sides and top of the HBM chip. This confirms that reducing HBM chip bending stress and chip module warpage can effectively mitigate crack formation. However, experimental results presented some unexpected findings. Although UF-02 exhibited the lowest bending stress and chip module warpage, cracks were still observed in its chip module. On the other hand, no cracks were observed in the chip module containing UF-03, suggesting that other factors beyond bending stress and warpage play a role in crack formation.

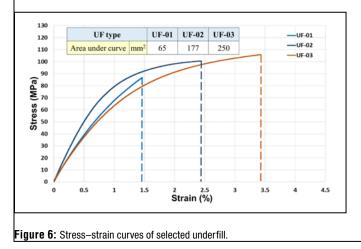

The stress-strain characteristics of the underfill materials are shown in **Figure 6**. The calculated areas under the stress-strain curve for UF-01, UF-02, and UF-03 were 65, 177, and 250mm<sup>2</sup>, respectively. A large area under the curve reflects higher ductility and elongation. Whereas a smaller area indicates brittleness and increased fracture risk. Based on this, UF-03,

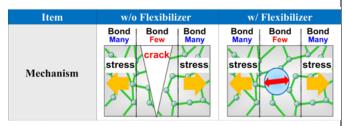

which exhibited the largest area under the curve, demonstrated the best suitability as an underfill material for HI-FOMCM applications. From the perspective of material properties, UF-02 was initially expected to exhibit higher ductility and elongation than UF-03 due to its lower Tg and modulus. However, contrary to expectations, the experimental results revealed the opposite. Further analysis showed that UF-03 was mixed with flexibilizers, enhancing its inherent elasticity and significantly improving its ductility and elongation. This improvement reduced internal stress within the material and prevented crack formation, as illustrated in **Figure 7**.

Figure 7: Crack mechanism by stress with and without a flexibilizer.

To ensure the reliability of UF-03, SEM cross sections of the chip modules containing UF-03 were analyzed after various reliability tests, including MSL3 + uHAST (96h), MSL3 + TCT (700 cycles), and HTSL (1000h). The results, shown in **Figure 8**, indicated no cracks were observed under these conditions. These findings confirm that chip modules

To learn more, visit <u>www.PlasmaEtch.com</u> or call us today at **775-883-1336**

| Reliability Item | UF-03                |                                |

|------------------|----------------------|--------------------------------|

| Kenability Hem   | Left                 | Right                          |

| MSL3+uHAST96     | HBM chip Chip        | Chip EMC                       |

|                  |                      | UE ********                    |

| MSL3+TCT700      | HBM chip EMC Chip    | Chip EMC HBM chip              |

| MSL3+1C1700      |                      | untion of and the same content |

|                  | HBM chip Chip<br>EMC | Chip EMC HBM chip              |

| HTSL1000         | UF                   | UF #######                     |

Figure 8: Cross section of UF-03 as observed using a SEM after the reliability assessment.

with UF-03 can pass all reliability tests, making it a suitable underfill material for high-performance chip modules.

The findings of this study emphasize the importance of selecting underfill materials not only based on mechanical stress reduction, but also on intrinsic material properties, such as ductility and elasticity. The incorporation of flexibilizers in UF-03 demonstrated the potential of enhancing material performance by modifying its composition. This suggests that future material designs could focus on tailored formulations to meet the specific demands of high-density semiconductor packages.

#### **Summary**

This study investigated the mechanical performance and reliability of three underfill materials (UF-01, UF-02, and UF-03) for packaging of HI-FOMCMs. Key findings from the research are as follows:

1. UF-01: Despite its high modulus and use in current applications, UF-01 exhibited cracks originating from the underfill area at the bottom of the HBM chip during MSL3 reliability testing. These cracks extended to the sides and top

of the chip, indicating insufficient flexibility and ductility to withstand thermal and mechanical stresses.

- 2. UF-02: Although UF-02 exhibited the lowest warpage and bending stress, cracks were still observed during reliability tests. This finding highlights that factors beyond warpage and stress, such as material ductility and elongation, significantly impact crack prevention.

- 3. UF-03: UF-03 demonstrated superior performance, passing all reliability tests, including MSL3, uHAST, TCT, and HTSL, without forming cracks. The inclusion of flexibilizers in its formulation enhanced its ductility and elongation, reducing stress and preventing crack formation.

These results emphasize the importance of selecting underfill materials with low modulus and high ductility for use in HI-FOMCMs. Materials like UF-03 that exhibit a larger area under the stress-strain curve provide greater resistance to stressinduced damage.

#### References

- W. Y. Teng, J. Lee, H. M. Tseng, L. Y. Hung, D. S. Jiang, Y. P. Wang, "Stress and reliability challenges of underfills in large-size fan-out multichip module packages," International Conf. on Electronics Packing (ICEP), 2022, p. 09.

- W. Y. Teng, C. C. Chen, F. L. Tsai, L. Y. Hung, D. S. Jiang, Y. P. Wang, "Effect of underfill additive agents on crack prevention in large fan-out multi-chip module packages," IEEE 24th Electronics Packaging Tech. Conf. (EPTC), 2022, p. 199.

- H. J. Lin, V. Lin, J. Lin, Y. J. Lu, D. Wang, Y. P. Wang, "High reliability solution of 2.5D package technologies," IEEE 23rd EPTC, 2021, pp. 620-623.

- H. Yamaguchi, T. Enomoto, T. Sato, "Stress variation analysis during curing process of epoxy underfill," ICEP, 2014, pp. 507-510.

- 5. O. Suzuki, "Recent advances in underfill for new package architectures," Pan Pacific Microelectronics Symp. (Pan Pacific), 2020.

- C. C. Tuan, K. S. Moon, C. P. Wong, "Polysiloxanebased surface modification of silica fillers for low stress underfill," IEEE 66th Electronic Components and Technology Conf. (ECTC), 2016, pp. 2569-2574.

- Y. C. Hu, Y. M. Liang, H. P. Hu, C. Y. Tan, C. T. Shen, C. H. Lee, S. Y. Hou," CoWoS architecture evolution for next generation HPC on 2.5D system in package," IEEE 73rd ECTC, 2023, pp. 2569-2574.

- 8. G. L. Zhao, H. L. Lin, X. H. Peng, Y. Y. Yang, X. C. Cheng Yu, G. Li, et al., "The factors influencing underfill's reliability in large-size packages," IEEE 73rd ECTC, 2023, pp. 1627-1632.

#### **Biographies**

Liang-Yih (Joe) Hung is a Department Manager of Corporate R&D at Siliconware Precision Industries Co., Ltd., Taichung, Taiwan, R.O.C. He received a Masters Degree from the Department of Materials Science & Engineering at National Chung Hsing U., Taiwan. He joined SPIL in 2002 and is in charge of new material development for advanced packaging applications; Email joe65@SPIL.com.tw

Chia-Wei Chang is a Senior Engineer in Corporate R&D at Siliconware Precision Industries Co., Ltd., Taichung, Taiwan, R.O.C. He received a Masters Degree from the Department of Chemistry National Sun Yat-Sen U., Taiwan. He joined SPIL in 2024 and is in charge of new material development for advanced packaging applications.

## smiths interconnect

# Cutting-edge Connectivity DaVinci Micro Test Socket

The coaxial structure of the DaVinci Micro test socket provides ideal pin to pin isolation reducing the effect of cross talk during testing. This allows for at speed functional testing of your IC.

- Controlled impedance interface

- Spring probe technology with homogenous alloy, protects against solder build up and increased probe life

- Optimized for power integrity of DUT

- Patented insulated metal socket housing provides un-matched mechanical strength

- For use with manual test, bench test and HVM Production testing using the same socket

DaVinci Micro inherits the DaVinci coaxial technology for IC applications to 350µm pitch. DaVinci Micro's fully shielded signal path negates the effects of cross-talk during testing, allowing an immediate yield enhancement over non-DaVinci products.

High Speed Digital

### Memory

# DECA

## thinkdeca.com

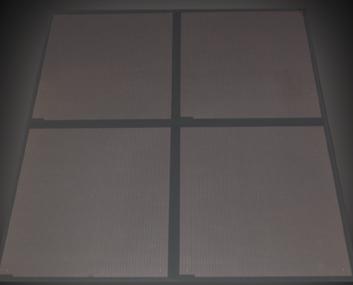

Realizing the full value of sem: standard 600mm square panels

## Initial format for 300mm test

designed to utilize existing industry 300 mm probe capacity

## Current optimized format

full 600mm active area for maximum utilization

# New package solutions for automotive optical sensors

By Weilung Lu, Adrian Arcedera, WonBae Bang, KiDong Sim [Amkor Technology, Inc.]

utomotive optical sensors, including cameras, image sensors, and light detection and ranging (LiDAR) components, are fundamental to the operation of advanced driver assistance systems (ADAS). These sensors play a crucial role in detecting and interpreting the vehicle's surroundings, supplying high-precision data necessary for ADAS functionality. With the evolution of autonomous driving technology, particularly the transition from the Society of Automotive Engineers (SAE) SAE J3016 Level 2 autonomy to Levels 4 and 5, the number of cameras and optical sensors integrated into each vehicle is expected to rise substantially. Industry projections, including those from SAE, suggest that future vehicles could be equipped with 8 to 10 or more cameras per unit.

The widespread adoption of ADAS by automotive manufacturers has significantly enhanced driving safety. These systems provide real-time assistance to drivers, reducing the likelihood of accidents and improving overall road safety. Key ADAS features include adaptive cruise control, lane departure warning, and automatic emergency braking, which have become standard in modern vehicles. As the industry progresses towards increased vehicle automation, the integration of ADAS technologies is accelerating, driving rapid advancements in sensor technology.

Beyond conventional camera-based applications, a range of innovative optical sensor technologies is emerging, further augmenting vehicle performance, safety, and user experience. For instance, ambient light sensors are increasingly integrated into vehicle systems to enhance both safety and comfort. These sensors adjust in-car lighting-including dashboard and console illumination-by detecting external light intensity, thereby improving visibility. They also regulate headlight activation in response to surrounding light conditions, ensuring optimal illumination in low-light environments. With ADAS requiring precise visual feedback, ambient light sensors contribute to a more adaptive, efficient, and user-friendly incabin experience.

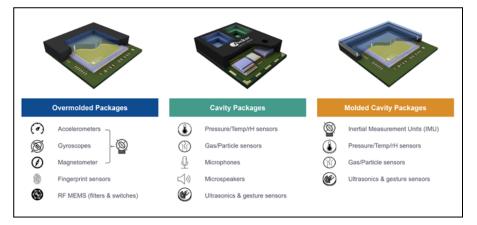

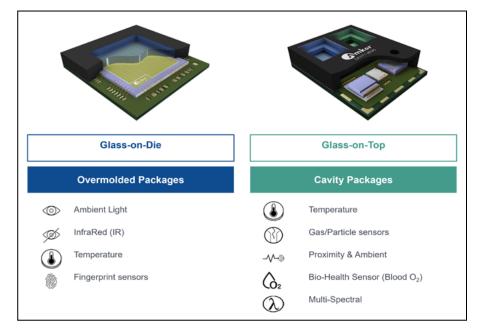

This article introduces the development of a new optical ball grid array (OBGA) packaging platform designed for automotive applications, with a focus on platform development and compliance with the Automotive Electronics Council (AEC) AEC-Q100 Grade 2 reliability standard. The proposed packaging solution extends beyond traditional cavity OBGA packages, which have been primarily utilized for microelectromechanical systems (MEMS) and sensor applications as illustrated in **Figure 1**.

The cavity OBGA platform, depicted in **Figure 2**, represents a well-established and mature technology that is currently in production for consumer electronics. The introduction of this new OBGA package marks a strategic expansion into automotive optical sensors. This initiative strengthens the company's competitive edge by aligning with the increasing

Figure 1: MEMS and sensor packages and applications.

Figure 2: Imaging, optical MEMS and sensing packages and applications.

demand for advanced sensor integration in modern vehicles.

The new OBGA packaging aims to expand the current portfolio by enhancing performance and reliability. Two key technological advancements drive innovation in this packaging platform. The first involves the adoption of glass-onsensor (GoS) technology, which facilitates the evaluation of clear die attach film (DAF) transmittance while ensuring automotivegrade reliability. This approach enables the package structure to meet the stringent performance and durability requirements demanded by the automotive sector. The second advancement introduces the glasson-mold (GoM) design, replacing traditional metal or liquid crystal polymer (LCP) lids commonly used in MEMS packaging. This modification eliminates the need for venting holes, effectively mitigating particle contamination in the sensor region. As a

# Bringing tomorrow's electronics to life with the 1µm ultra high speed die bonder

result, the optical sensor's reliability and performance are significantly improved.

Designed specifically for automotive optical sensor products, the new OBGA package has undergone comprehensive feasibility studies and rigorous reliability testing. These assessments confirm its structural robustness and suitability for demanding automotive environments, ensuring that the package can withstand extended operational lifecycles and harsh environmental conditions. To address these challenges, advanced toolbox and open tooling capabilities are leveraged to ensure that design for cost (DFC) and design for manufacturability (DFM) considerations are integrated from the initial stages of product development. Prioritizing manufacturing efficiency and scalability allows the delivery of high-performance optical sensor packaging solutions that meet the evolving requirements of the automotive industry.

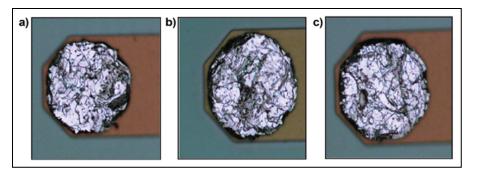

#### New package development

To overcome the challenges associated with existing packaging solutions, the new OBGA package integrates advanced molding and lid placement technologies commonly employed in MEMS cavity products. The proposed OBGA package serves as an alternative solution designed to provide enhanced mechanical robustness, accommodating larger sensor sizes anticipated in next-generation automotive applications.

The new OBGA package leverages extensive expertise in cavity MEMS packaging, combined with a proven track record in managing high-end consumer digital camera product lines. This synergy results in a highly reliable and manufacturing-efficient package that meets the stringent performance and durability requirements of the automotive industry. The integration of these advanced technologies ensures that the package maintains structural integrity and optical performance, even under harsh environmental conditions typical of automotive applications.

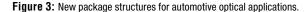

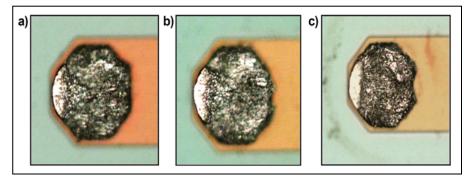

Two distinct OBGA package variants are shown in **Figure 3**, each designed to address specific application needs. The first variant, GoS, features a compact footprint and is derived from consumer optical fingerprint sensor (FPS) technology. This solution utilizes an established material set and incorporates film assisted molding (FAM) technology, which has been successfully implemented in the existing product portfolio. The second variant, GoM, represents a completely new design, developed from the ground up to meet the specific demands of automotive optical sensor applications. This innovative structure offers enhanced performance and greater integration capabilities, ensuring long-term reliability and optimal functionality within ADAS and autonomous vehicle ecosystems.

#### **Glass-on-sensor development**

The glass-on-sensor configuration involves laminating a transparent die attach film with glass and directly stacking the glass onto the sensor die. A critical characteristic of this structure is the absence of any gap between the sensor and the DAF, ensuring seamless optical transmission. Given the importance of optical clarity in sensor performance, evaluating the material properties of DAF for optimal transmittance and thermal stability is a crucial step in the development process.

Optical transmittance and thermal durability of DAF materials are essential for optoelectronic applications, including automotive sensors, display technologies, and optical coatings. The development process assessed transparent die attach films used in GoS packaging, with particular emphasis on their transmittance characteristics and long-term stability under thermal stress.

Three candidate materials—Material A, Material B, and Material C—were selected for evaluation. Film thickness and thermal curing conditions were evaluated for their influence on optical performance. Key parameters, including transmittance across the visible light spectrum (400–700nm) and stability after thermal aging, were analyzed. A detailed summary of the material properties and corresponding performance data is presented in **Table 1**.

Identifying materials capable of maintaining high optical transmittance while withstanding prolonged thermal stress is a critical requirement for applications demanding long-term reliability and performance. To simulate assembly process operating conditions, the selected materials underwent thermal aging at 175°C for 8 hours. This process was designed to assess their ability to sustain optical integrity and performance stability under extended high-temperature exposure.

The experimental procedure began with the lamination of DAF onto glass

substrates at 65°C, followed by an initial optical transmittance evaluation within the 400-700nm wavelength range. The materials were then subjected to thermal aging at 175°C for 8 hours and transmittance measurements were conducted again to analyze any degradation or shifts in optical performance after thermal treatment.

These tests were performed on materials with two distinct film thicknesses— $10\mu m$  and  $20\mu m$ —to assess how thickness variations influence transmittance retention and thermal stability.

Table 2 presents the transmittance results for the different materials across various wavelengths following thermal aging at 175°C for 8 hours. Among the evaluated

Stacked glass

Small footprint

| Material | Thickness | Тg | CTE | Film Type | Appearance         |

|----------|-----------|----|-----|-----------|--------------------|

| А        | 10 µm     | 41 | 81  | Silica    | Transparent (>90%) |

| В        | 20 µm     | 62 | 75  | Silica    | Transparent (>90%) |

| с        | 20 µm     | 15 | 49  | Silica    | Transparent (>90%) |

Table 1: Technical property data.

| Wavelength (nm)  | Material A | Material B | Material C |

|------------------|------------|------------|------------|

| Red (610–700)    | 99.99%     | 99.44%     | 94.6%      |

| Orange (590–610) | 99.71%     | 99.28%     | 93.2%      |

| Yellow (570–590) | 99.58%     | 98.28%     | 92.4%      |

| Green (500–570)  | 99.45%     | 97.97%     | 90.7%      |

| Blue (450–500)   | 98.45%     | 95.65%     | 90.2%      |

| Purple (400–450) | 96.34%     | 91.33%     | 88.9%      |

Table 2: Transmittance results after thermal cure at 175°C for 8 hours.

materials, Material A demonstrated superior transmittance across nearly all wavelengths, outperforming the other candidates. Additionally, the results indicate that thinner films ( $10\mu m$ ) exhibited higher transmittance compared to thicker films ( $20\mu m$ ), confirming the influence of film thickness on optical efficiency.

Both Material A and Material B maintained excellent optical transmittance, consistently exceeding 90% in the 400–700nm wavelength range after undergoing thermal aging. This high retention of transmittance highlights their robust optical stability under extended heat exposure—a critical requirement for automotive optical sensor applications.

| Package       | Glass-on-Sensor<br>OBGA Test Vehicle |

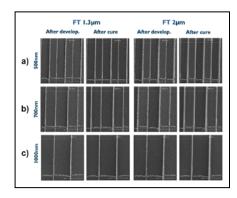

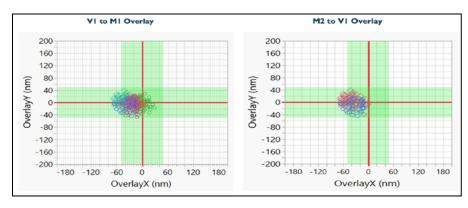

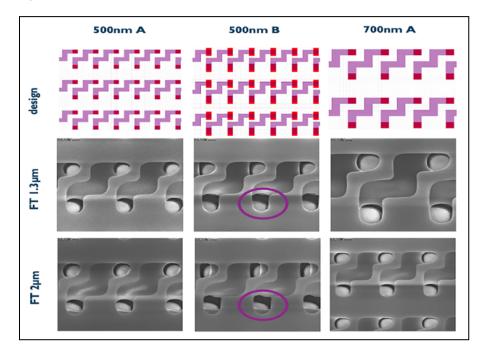

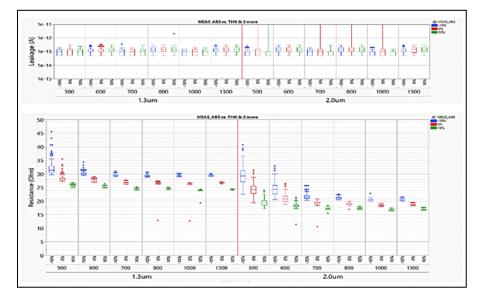

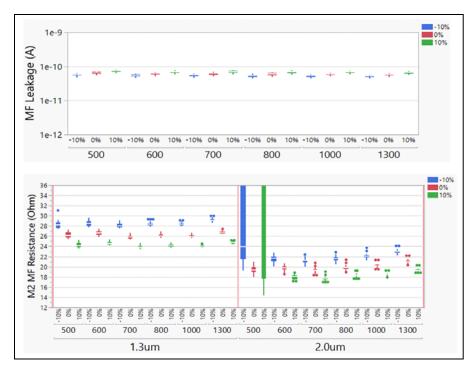

|---------------|--------------------------------------|